dq-Transformation IP core#

Transforms three input quantities from a three phase system to dq-coordinates

Input interface is PL-only

Transformation can only be triggered by a PL signal, but not by the software driver

Output is supplied to PL-ports as well as AXI4-Lite

Inputs have to be fixed point and match the interface description of Interface of dq-Transformation IP Core

The inputs are transformed on each rising edge on the IP core input

CurrentValid_indq_Doneindicates that the output values are valid to subsequent IP cores

Table Interface of dq-Transformation IP Core lists all input and output ports (AXI and external port) that are present in the IP core.

Port Name |

Port Type |

Data Type |

Target Platform Interfaces |

Range |

Unit |

Function |

|---|---|---|---|---|---|---|

i_ph1 |

Input |

sfix18_En11 |

External Signal |

+/-64 |

A |

phase current 1 |

i_ph2 |

Input |

sfix18_En11 |

External Signal |

+/-64 |

A |

phase current 2 |

i_ph3 |

Input |

sfix18_En11 |

External Signal |

+/-64 |

A |

phase current 3 |

theta |

Input |

sfix24_En20 |

External Signal |

+/-8 |

rad |

electrical motor angle |

theta_offset_AXI |

Input |

sfix24_En20 |

AXI4-Lite |

+/-8 |

rad |

offset of angle sensor |

current_valid_in |

Input |

bool |

External Signal |

trigger ip core calculation |

||

i_d |

Output |

sfix18_En11 |

External Signal |

+/-64 |

A |

current in d-axis |

i_q |

Output |

sfix18_En11 |

External Signal |

+/-64 |

A |

current in q-axis |

i_d_AXI |

Output |

sfix18_En11 |

AXI4-Lite |

+/-64 |

A |

current in d-axis |

i_q_AXI |

Output |

sfix18_En11 |

AXI4-Lite |

+/-64 |

A |

current in q-axis |

dq_done |

Output |

bool |

External Signal |

rising edge if ip core calculation finished |

||

sin |

Output |

sfix16_En14 |

External Signal |

+/-2 |

sine value of angle (+/- 1) |

|

cos |

Output |

sfix16_En14 |

External Signal |

+/-2 |

cosine value of angle (+/- 1) |

|

i_1_AXI |

Output |

sfix18_En11 |

AXI4-Lite |

+/-64 |

A |

phase current 1 |

i_2_AXI |

Output |

sfix18_En11 |

AXI4-Lite |

+/-64 |

A |

phase current 2 |

i_3_AXI |

Output |

sfix18_En11 |

AXI4-Lite |

+/-64 |

A |

phase current 3 |

Vitis#

Initialize one driver instance and read output:

static struct uz_dqIPcore_config_t config={

.base_address= BASE_ADDRESS,

.ip_clk_frequency_Hz=IP_CORE_FRQ,

.theta_offset = -1.5f // add your encoder offset here!

};

uz_dqIPcore_t* test_instance = uz_dqIPcore_init(config);

struct uz_dq_t currents = uz_dqIPcore_get_id_iq(test_instance);

Warning

The software driver has no way to read the trigger transformation signal CurrentValid_in nor the output valid signal dq_Done! Thus, the user has to be sure that a transformation took place and is finished. This means that the driver can mostly be used for debugging control algorithms that are fully implemented in the PL!

Driver reference#

-

typedef struct uz_dqIPcore_t uz_dqIPcore_t#

Object data type definition of the dq IP-Core driver.

-

struct uz_dqIPcore_config_t#

-

uz_dqIPcore_t *uz_dqIPcore_init(struct uz_dqIPcore_config_t config)#

Initialize an instance of the driver for the dq-IP-Core.

- Parameters:

config – Configuration struct for the instance

- Returns:

uz_dqIPcore_t* Pointer to an initialized instance of the driver

-

uz_3ph_dq_t uz_dqIPcore_get_id_iq(uz_dqIPcore_t *self)#

Read the output currents id and iq from the IP-Core and return them.

- Parameters:

self – Pointer to driver instance

- Returns:

uz_dq_t

-

uz_3ph_abc_t uz_dqIPcore_get_i_abc(uz_dqIPcore_t *self)#

Read the input currents i1, i2, and i3 from the IP-Core and return them.

- Parameters:

self – Pointer to driver instance

- Returns:

uz_3ph_abc_t

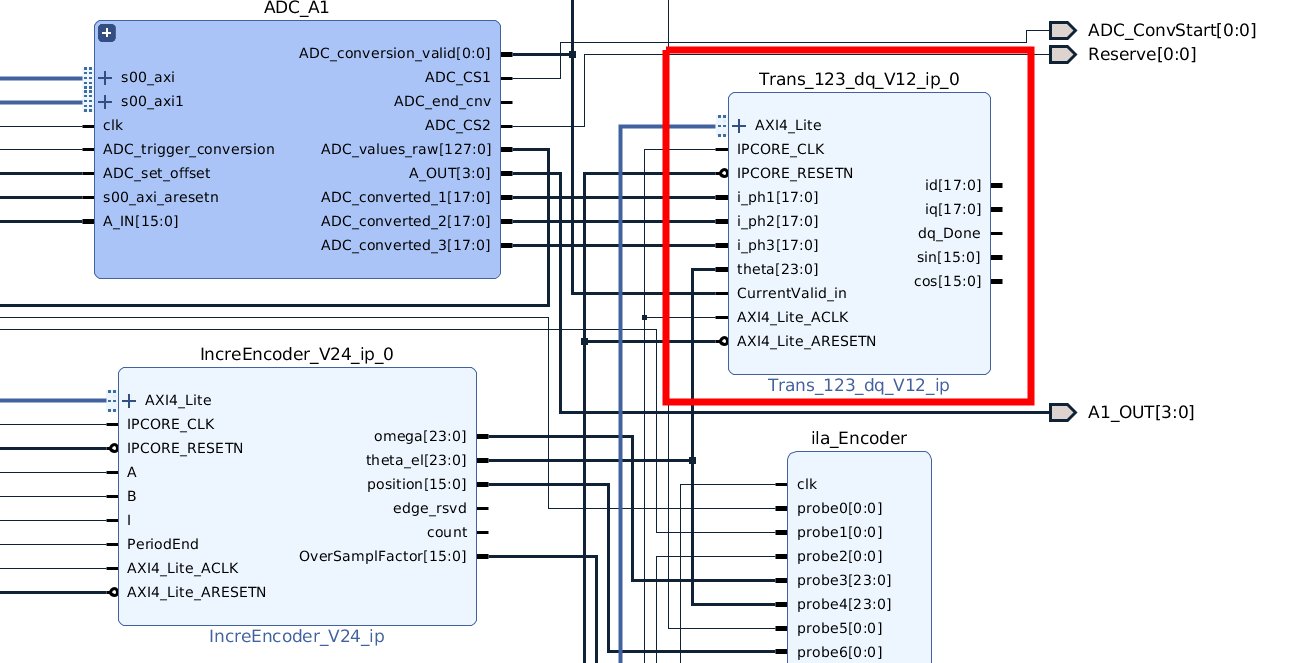

Vivado#

The only tested clock frequency for IPCORE_CLK and AXI4_Lie_ACLK is 50 Mhz.

Port Name |

CLK |

Usage |

|---|---|---|

AXI4_Lite |

50 MHz |

Connect to AXI_smartconnect |

IPCORE_CLK |

50 MHz |

Connect to 50 MHz clock |

IPCORE_RESETN |

50 MHz |

Connect to 50 MHz reset |

AXI4_LiteACLK |

50 MHz |

Connect to IPCORE_CLK |

AXI4_Lite_ARESETN |

50 MHz |

Connect to IPCORE_RESETN |