Mux Axi / ISR Trigger Control#

Selects the PWM counter event that triggers ADC and the interrupt of the R5 processor

Selects ADC/ISR trigger ratio: trigger the ISR in the R5 every n-th ADC trigger event

(n = 1,2,3,...)Adds an optional delay to the ADC trigger path

PWM counter events#

The

PWM and SS Controlas well as the 3-level PWM IP core use an up-down counterAt counter min and max those IP cores provide rising edge signals that are fed to the uz_mux_axi IP core

Those trigger signals depend on the selected PWM frequency

Interrupt sources#

The user selects the PWM trigger source for ADC triggering via

INTERRUPT_ISR_SOURCE_USER_CHOICEinuz_global_configuration.h(see Global configuration)The trigger mode for the ISR is controlled by

INTERRUPT_ISR_TRIGGER_ON_ADC_DATA_READY(see R5 interrupts):0: ISR fires directly on the selected PWM event1: ISR fires onaxi2tcm_write_done(ADC conversion complete + data in TCM), eliminating the race condition between ADC data transfer and ISR execution

Below, as well as in

uz_global_configuration.h, the user will find the valid PWM interrupt source options:

/** ISR trigger source (PWM counter event, used for ADC triggering and as base for the ISR trigger)

*

* 0 for Interrupt_2L_max_min

* 1 for Interrupt_2L_min

* 2 for Interrupt_2L_max

* 3 for Interrupt_3L_start_center

* 4 for Interrupt_3L_start

* 5 for Interrupt_3L_center

*/

#define INTERRUPT_ISR_SOURCE_USER_CHOICE 0U

/** ISR trigger mode: 0 = direct PWM event, 1 = axi2tcm_write_done (ADC data ready in TCM) */

#define INTERRUPT_ISR_TRIGGER_ON_ADC_DATA_READY 1U

ADC/ISR trigger ratio#

If necessary, the user can choose an integer multiple ratio between ADC and ISR triggering

This is done by setting the

INTERRUPT_ADC_TO_ISR_RATIO_USER_CHOICE#defineinuz_global_configuration.h

ADC trigger delay#

If necessary, the user can add an additional delay to the ADC trigger path

This is done by setting

ADC_TRIGGER_DELAY_IN_USinuz_global_configuration.hThe configured delay value is applied by the

delay_triggerblock in the PL. For the block behavior, see Delay Trigger Block in R5 interrupts.This delay applies in both ISR trigger modes (

INTERRUPT_ISR_TRIGGER_ON_ADC_DATA_READY= 0 or 1): the ADC is always triggered by the selected PWM source, and whenINTERRUPT_ISR_TRIGGER_ON_ADC_DATA_READY = 1the ISR fires after the delayed ADC conversion completes

Example#

The user wants to have a PWM frequency of 100 kHz, an ISR frequency of 20 kHz, and an ADC trigger delay equal to half the PWM deadtime:

The user selects the PWM frequency of 100 kHz: the define

UZ_PWM_FREQUENCYis set to100.0e3finuz_global_configuration.hThe trigger source is

Interrupt_2L_min: the defineINTERRUPT_ISR_SOURCE_USER_CHOICEis set to1Uinuz_global_configuration.hThe trigger ratio is set to 5 (100 kHz/20 kHz = 5): the define

INTERRUPT_ADC_TO_ISR_RATIO_USER_CHOICEis set to5Uinuz_global_configuration.hThe ADC trigger delay is set to

UZ_PWM_DEADTIME_IN_US/2inuz_global_configuration.h, i.e.0.15 us

#define INTERRUPT_ISR_SOURCE_USER_CHOICE 1U

#define INTERRUPT_ISR_TRIGGER_ON_ADC_DATA_READY 0U

#define INTERRUPT_ADC_TO_ISR_RATIO_USER_CHOICE 5U

#define UZ_PWM_FREQUENCY 100.0e3f

#define UZ_PWM_DEADTIME_IN_US 0.30f

#define ADC_TRIGGER_DELAY_IN_US (UZ_PWM_DEADTIME_IN_US/2)

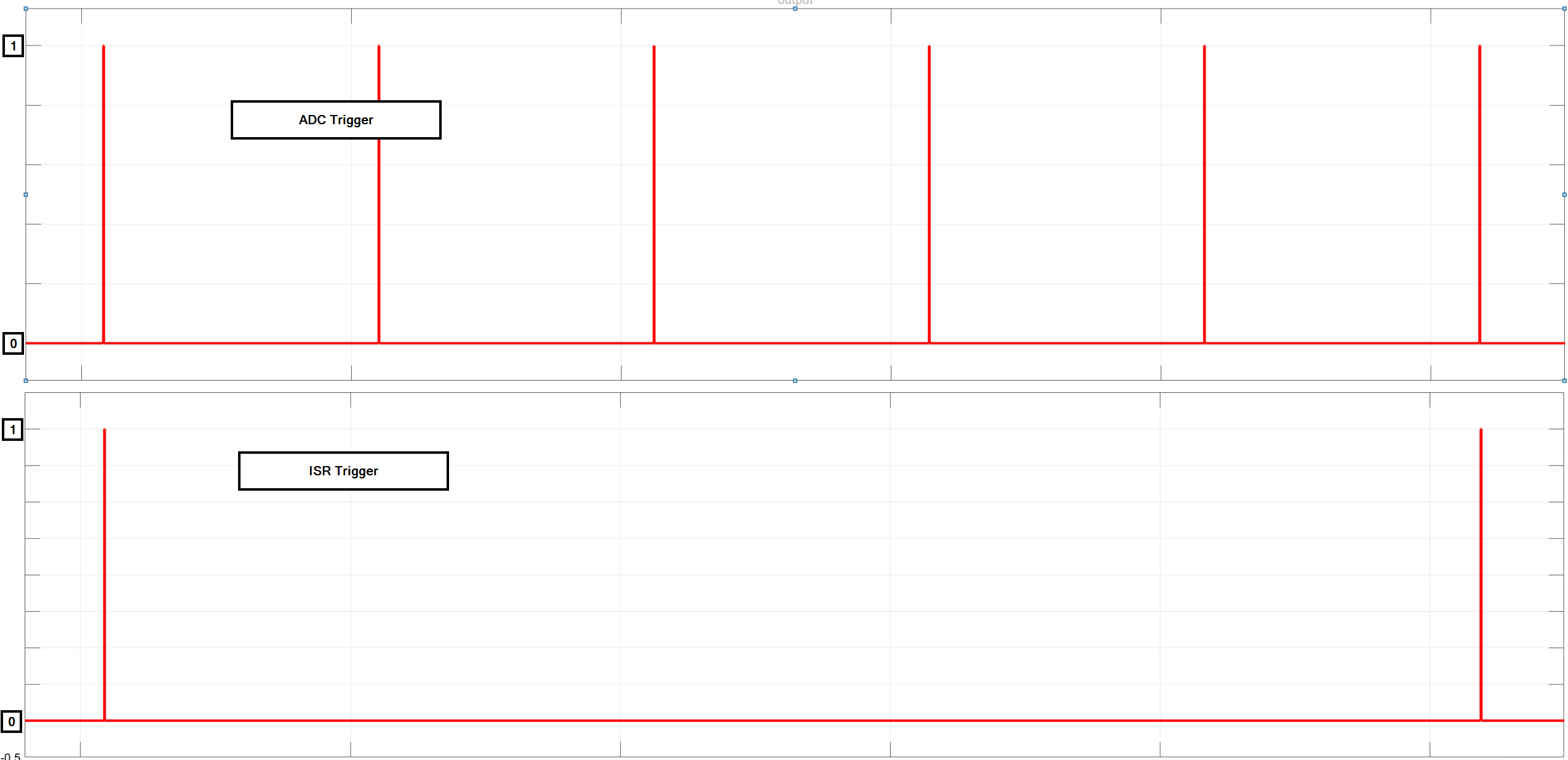

These settings result in the behavior depicted in Fig. 395 (ADC interrupt in the upper subplot, interrupt of R5 in the lower subplot):

Fig. 395 Resulting trigger ratio from the example above#

Warning

Trigger ratios other than

1were only tested with trigger sourceInterrupt_2L_minEspecially when using trigger sources with two ADC trigger events (e.g.

Interrupt_2L_max_min), the user has to take care of the resulting ADC/ISR trigger ratio

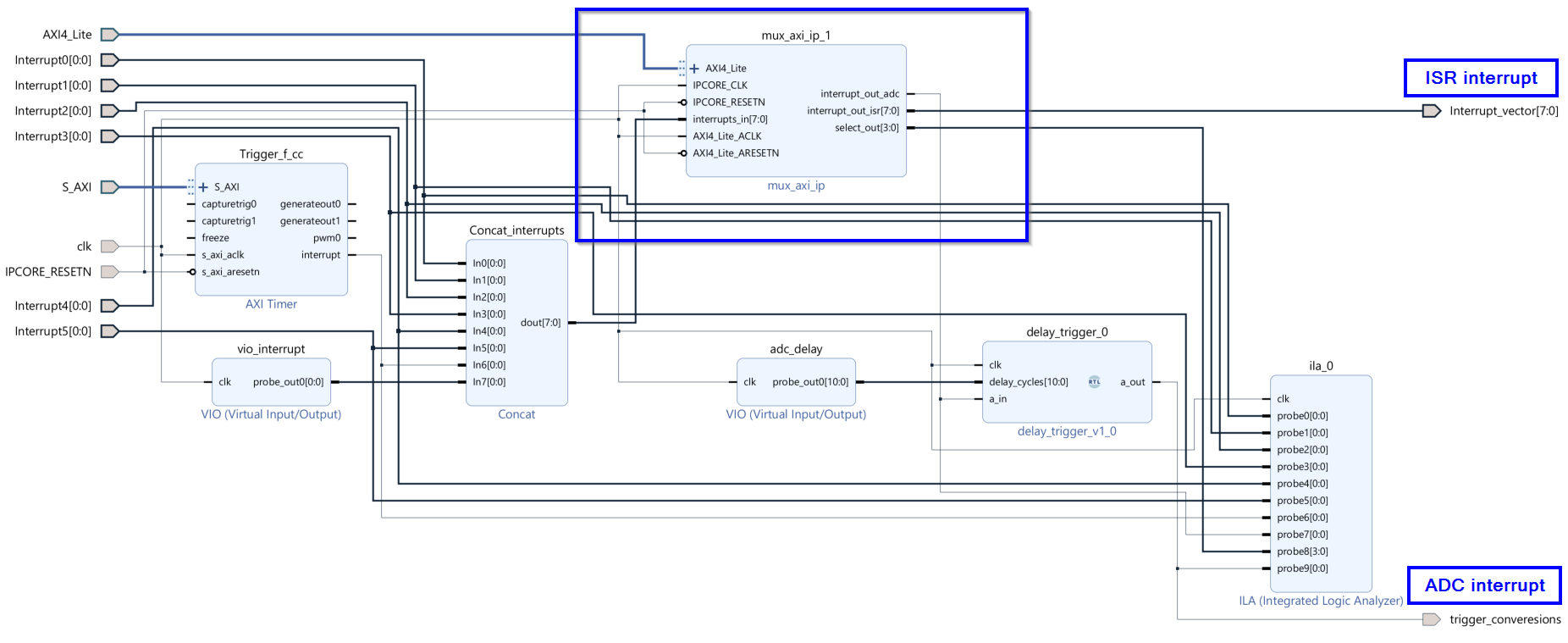

IP core#

The IP core takes up to 8 different interrupt sources as inputs (external port interrupts_in).

One of these inputs is selected by AXI configuration and routed directly routed to the interrupt_out_adc external port.

Additionally, all interrupt sources of interrupts_in are coupled with an internal counter that routes the signal of interrupts_in to interrupt_out_isr every n-th time the interrupt_out_adc signal is high.

An additional AXI register delays the ADC trigger output by 0 to 1023 IP-core clock cycles.

Table Interface of uz_mux_axi IP core lists all input and output ports (AXI and external port) that are present in the IP core.

Port Name |

Port Type |

Data Type |

Target Platform Interfaces |

Range |

Unit |

Function |

|---|---|---|---|---|---|---|

interrupts_in |

Input |

uint8 |

External Signal |

interrupt input vector |

||

interrupt_out_adc |

Output |

bool |

External Signal |

ADC trigger signal |

||

interrupt_out_isr |

Output |

bool |

External Signal |

ISR trigger signal |

||

select_out |

Output |

ufix4 |

External Signal |

0-6 |

selected mux number |

|

select_AXI |

Input |

uint32 |

AXI4-Lite |

0-6 |

mux selector |

|

select_n_th_adc_interrupt |

Input |

uint32 |

AXI4-Lite |

1-255 |

ADC/ISR trigger ratio |

|

delay_ADC_trigger_in_clk_cycles_AXI |

Input |

uint32 |

AXI4-Lite |

0-1023 |

clk cycles |

ADC trigger delay in clock cycles |

Fig. 396 of the IP core embedded in the block design:

Fig. 396 IP core in the default Vivado block design.#

Software driver#

The software driver is initialized by default. The user just has to select the mux, the interrupt ratio, and the ADC trigger delay in uz_global_configuration.h.

The IP core is initialized at the startup of the system. The software driver is not intended to change the settings at runtime.

Reference#

-

typedef struct uz_mux_axi_t uz_mux_axi_t#

Data type for object uz_mux_axi.

-

struct uz_mux_axi_config_t#

Configuration struct for uz_mux_axi.

Public Members

-

uint32_t base_address#

Base address of the IP-Core

-

uint32_t ip_clk_frequency_Hz#

Clock frequency of the IP-Core

-

uint32_t mux#

Select value for the mux

-

uint32_t n_th_interrupt#

Trigger ratio of adc_interrupt/isr_interrupt between 1 and 255

-

float delay_adc_trigger_in_us#

ADC trigger delay in us. Rounded up to 0..1023 clock cycles.

-

uint32_t base_address#

-

uz_mux_axi_t *uz_mux_axi_init(struct uz_mux_axi_config_t config)#

Initializes an instance of the uz_mux_axi driver.

- Parameters:

config – Configuration values for the IP-Core

- Returns:

Pointer to initialized instance

-

void uz_mux_axi_enable(struct uz_mux_axi_t *self)#

Enables the instance of the uz_mux_axi IP-Core.

- Parameters:

self – Pointer to IP-Core instance that was initialized with init function

-

void uz_mux_axi_set_mux(struct uz_mux_axi_t *self, uint32_t mux)#

Sets the mux value (selects the interrupt source)

- Parameters:

self – Pointer to IP-Core instance that was initialized with init function

mux – Value of the selected mux (see uz_global_configuration.h)

-

void uz_mux_axi_set_n_th_interrupt(struct uz_mux_axi_t *self, uint32_t n_th_interrupt)#

Sets the n_th_interrupt value (sets the interrupt ratio between adc_interrupt/isr_interrupt)

- Parameters:

self – Pointer to IP-Core instance that was initialized with init function

n_th_interrupt – Value that sets the ratio between adc_interrupt and isr_interrupt

-

void uz_mux_axi_set_delay_adc_trigger_in_us(struct uz_mux_axi_t *self, float delay_adc_trigger_in_us)#

Sets the ADC trigger delay in microseconds.

- Parameters:

self – Pointer to IP-Core instance that was initialized with init function

delay_adc_trigger_in_us – ADC trigger delay in us. Rounded up to 0..1023 clock cycles.