Vivado build Tcl scripts#

The default Vivado project (see Default Vivado project) can be generated using the build.tcl script.

Additionally, there are some helper scripts to facilitate the update of the build.tcl script after changes to the Vivado project are done.

Since these scripts are coupled with the paths in the ultrazohm_sw/vivado folder, they are not included in tcl_scripts (see Tcl Scripts) but located in ultrazohm_sw/vivado.

build.tcl#

Generates the UltraZohm Vivado project (ultrazohm.xpr).

Usage:

Open Vivado

Click on

Window->Tcl ConsoleA window on the bottom of Vivado appears (Tcl Console)

Navigate to the location of the

ultrazohm_swrepository on your local file system usingcdin the Tcl console (on Windows, wrap the path in{})Navigate to

ultrazohm_sw/vivadoin the Tcl consoleExample (Windows):

cd {C:\git\ultrazohm_sw\vivado}

Call build.tcl with:

source build.tcl

Calling the script leads to Vivado generating the project.

Fig. 66 Call build.tcl to build the Vivado project#

Note

The build.tcl script assumes that the UltraZohm is equipped with the TE0808 SoM with an UltraScale 9EG.

This is true for all standard UltraZohm systems, i.e., only special development systems at TH Nürnberg and TU München use other SoMs.

update_tcl_scripts_for_vc.tcl#

This script has to be called to incorporate changes to the default Vivado project into the build.tcl script.

Warning

Only call update_tcl_scripts_for_vc.tcl if the changed project was built using build.tcl.

Do not use it if you used another project or a project that was generated using build_selected_target.tcl!

Workflow:

Build Vivado project using

source build.tclMake changes to Vivado Project

Save project

Run

source update_tcl_scripts_for_vc.tclCommit the changes

modified: vivado/_build.tcl modified: vivado/bd/_zusys.tcl modified: vivado/bd/zusys.tcl modified: vivado/build.tcl modified: vivado/project/ultrazohm.xpr modified: vivado/project/zusys/zusys.bd

Generate bitstream

Export xsa via vivado_export_xsa.tcl.

Commit the changes

modified: vitis/vivado_exported_xsa/zusys_wrapper.xsa modified: vivado/DebugProbes.ltx

Fig. 67 Make a change in the Vivado default project and save it using update_tcl_scripts_for_vc. Note that this is just an example change.#

Compatibility with TE0803#

The default Vivado project is compatible with TE0808 (default with 9EG).

Additionally, TE0803 can be used.

Both SoMs are mostly pin compatible but some positive and negative pairs of differential signals that are used as LVDS for A1, A2, and A3 are swapped.

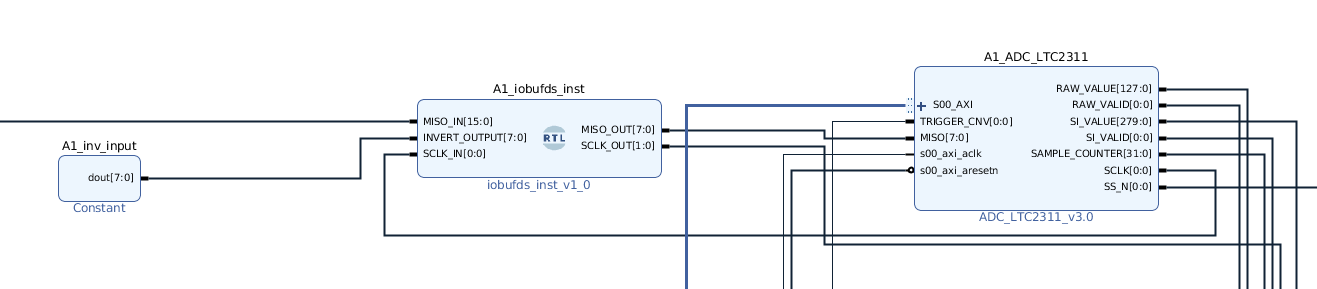

To achieve compatibility, an external IOBUF is used instead of the internal IOBUF of the ADC LTC2311 V3.

Depending on the board version, some of the signals are inverted using a magic constant (A1_inv_Input) that is set when generating the Vivado project according to the selected SoM (by build_selected_target.tcl).

Fig. 68 External IOBUF for ADC IP core and constant to invert signals depending on SoM (TE0808 or TE0803).#

build_selected_target.tcl#

Generates the UltraZohm Vivado project (ultrazohm.xpr) for a specified System-on-a-Module.

Tested are TE0803 with 2EG ("trenz.biz:te0803_2eg_1e:part0:1.0") and 3EG ("trenz.biz:te0803_3eg_1e:part0:1.0").

Before calling build_selected_target.tcl, the board_part has to be changed to the desired SoM:

set board_part "trenz.biz:te0803_2eg_1e:part0:1.0"