Controller in the Loop#

Controller in the loop (CIL) refers to a setup in which the implementation of a control algorithm is tested with a plant model that is implemented on the UltraZohm. This is useful to make sure that implemented algorithms work as intended before testing on real hardware. The following sections show multiple possibilities to implement on-chip CIL on the UltraZohm.

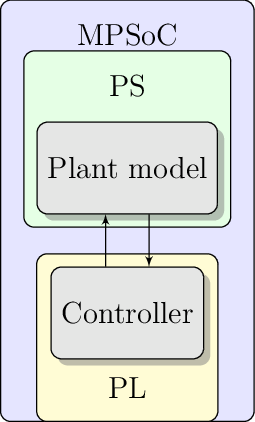

Fig. 30 Plant model in PS, Control algorithm in PL

Implementing the plant model in the PS and the control algorithm in the PL [1] is depicted in Fig. Fig. 30. This approach offers easy implementation of discretized plant models in C code. However, the sample time is limited to the range of kilohertz. The PS has to handle the interrupt, read from PL registers, and write back to them, resulting in an overhead of approximately \(1 \mu s\) [2]. Furthermore, the calculation time of the plant model increases for more complex or multiple plant models. Thus, this approach is favorable if the plant model is simple or the required sampling frequency does not exceed \(f_s=100 kHz\).

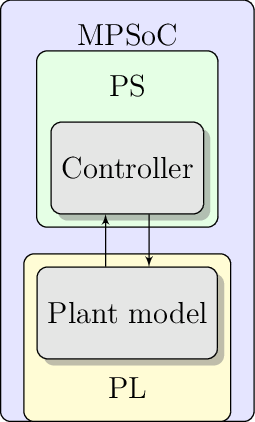

Fig. 31 Plant in PS, Control algorithm in PL

Fig. Fig. 31 shows the scheme that is recommended, which implements the plant model in the PL. Moving the plant model to the PL allows for higher sampling frequencies, frees the processor from calculating the model, and enables the emulation of more complex as well as multiple parallel plant models. Implementing IP cores on the FPGA is generally thought of as more challenging compared to writing code for the CPU. This is mitigated by using MATLAB HDL Coder, allowing easy integration into the UltraZohm FPGA design.

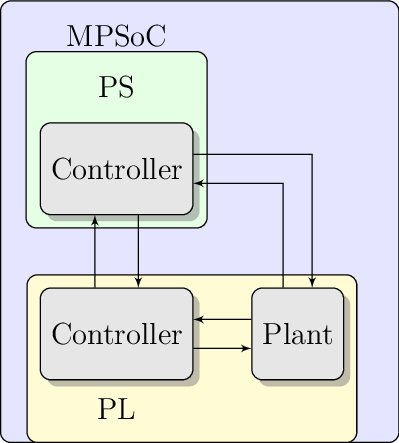

Fig. 32 Control algorithm in PS and PL, Plant model in PL

Simulating the plant model in the PL can also be used for control algorithms which are mapped to the PS as well as the PL to improve the usable computational performance, as shown in Fig. Fig. 32.

Hardware in the loop#

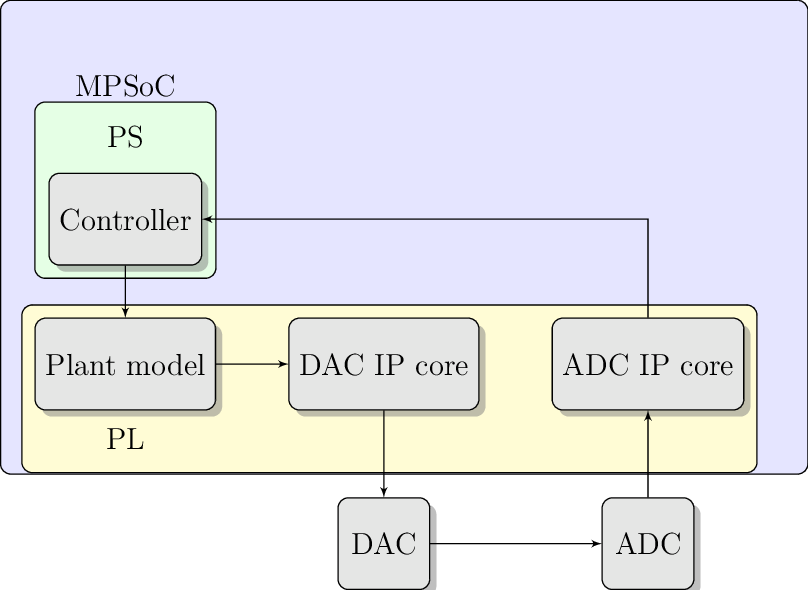

In addition to the CIL setup that closes the loop inside of the FPGA, Hardware in the Loop (HIL) closes the loop outside of the system. Specifically, the UltraZohm HIL concept uses the uz_dac8831 adapter card to close the loop directly with the ADC. See the following docs pages for more information:

Fig. 33 Plant in PS, Control algorithm in PL

Implemented PL Plant models#

The following IP cores are intended to be used for CIL: